Основные характеристики

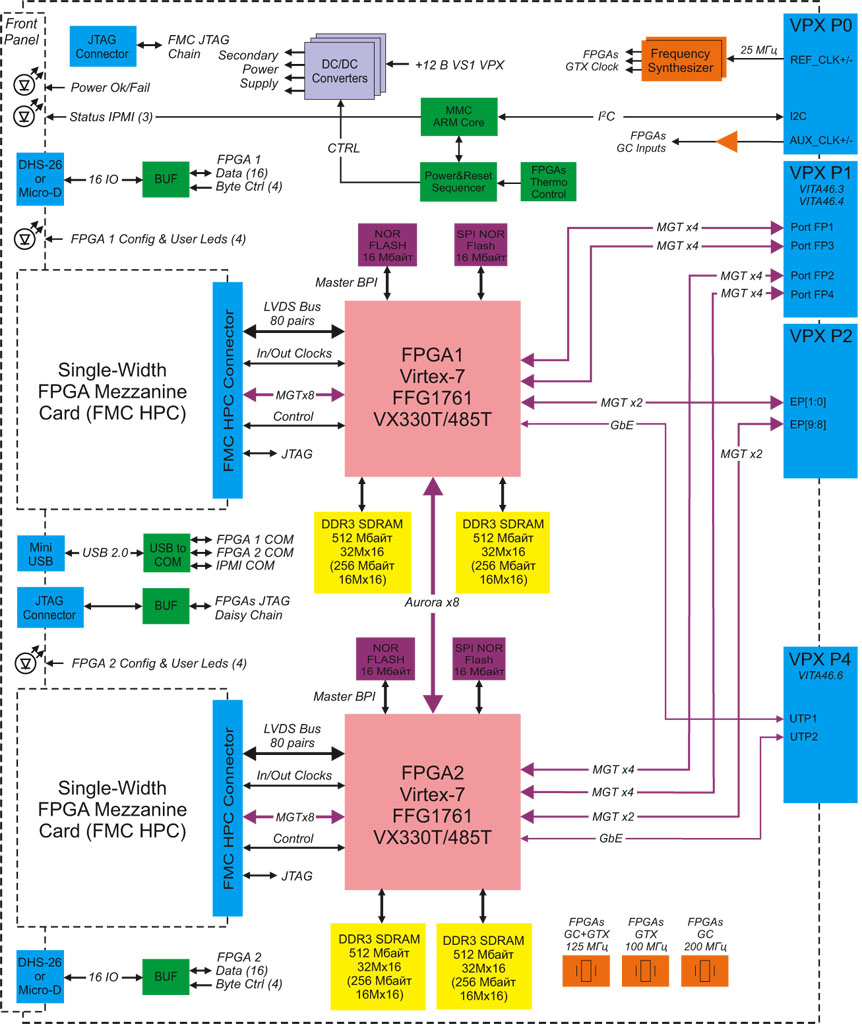

- Две высокопроизводительные FPGA Xilinx Virtex-7 в корпусе FFG1761

с поддержкой установки кристаллов XC7VX330T и XC7VX485T

- По два независимых 16-ти разрядных банка памяти DDR3-800

общим объёмом до 1 Гбайт на каждой FPGA

- Установка двух субмодулей FMC в соответствии со стандартом

ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard

с поддержкой HPC интерфейса, включая 8 дуплексных линий MGT

- Модуль форм-фактора VPX 6U, соответствующий стандартам:

ANSI/VITA 46.0-2013 (воздушное охлаждение),

ANSI/VITA 46.3-2012,

ANSI/VITA 46.4-2012,

ANSI/VITA 46.6-2013,

ANSI/VITA 57.1-2010

и ANSI/VITA 65-2010 (R2012)

- Поддержка системных интерфейсов: PCIe, SRIO, Gigabit Ethernet,

XAUI (отдельно приобретаемые IP-ядра)

- Исполнение с воздушным охлаждением

Описание

Особенности

Модуль SVP-723 форм-фактора VPX 6U разработан на базе высокопроизводительной

серии FPGA Xilinx Virtex-7 и сочетает в себе широкие интерфейсные возможности

и большой объём встроенной скоростной памяти. Поддержка установки двух субмодулей FMC

стандарта ANSI/VITA 57.1-2010 FPGA Mezzanine Card (FMC) Standard

позволяет гибко организовать ввод/вывод необходимых пользователю сигналов, включая

аналоговые (с использованием субмодулей АЦП/ЦАП), оптические и цифровые.

Модуль SVP-723 предназначен для приложений, требующих предельно высокую

производительность цифровой обработки данных в реальном времени: фильтрации, спектральных

преобразований, корреляционной обработки, кодирования/декодирования, работы с пакетами

и т. д. Так, пиковая производительность обработки операций на целочисленных операциях

умножить-аккумулировать достигает 2000 млрд./с (операнды 25 × 18 бит,

аккумулятор 48 бит) для каждой FPGA, а производительность обмена FPGA с памятью

DDR3 превышает 3 Гбайт/с.

Производительность

Пропускная способность системных интерфейсов модуля (FP 1–4) превышает 128 Гбит/с

(16 MGT 8 Гбит/с на двух FPGA), поддерживается широкий ряд стандартов:

PCIe вплоть до версии 3.0 (только для VX330T), SRIO, XAUI, Gigabit

Ethernet, которые, в зависимости от типа коммутаторов и объединительных плат, могут сочетаться

между собой в различных комбинациях (реализация интерфейсов осуществляется с помощью

IP-ядер, приобретаемых отдельно).

Модуль поддерживает кольцевое соединение в составе крейта через линии EP[1:0] и EP[9:8]

разъёма VPX P2 со скоростью до 25 Гбит/с.

Дуплексная пропускная способность межкристального обмена FPGA модуля превышает

50 Гбит/с (8 MGT Virtex-7 по 6,25 Гбит/с).

Пропускная способность интерфейса каждой FPGA модуля с субмодулем FMC достигает

80 Гбит/с через шины LVDS и 50 Гбит/с на приём/передачу через каналы MGT

Virtex-7 (8 полнодуплексных линий по 6,25 Гбит/с). Обеспечена поддержка широкой

номенклатуры стандартизованных субмодулей FMC производства ЗАО «Скан

Инжиниринг Телеком» и сторонних производителей.

Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через

объединительную плату, географическая адресация и т. д., значительно облегчает интеграцию модуля

во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных

и военных применений.