Основные характеристики

- Высокопроизводительная FPGA Xilinx Virtex-6

семейства LXT или SXT

- Четыре независимых 16-ти битных банка памяти DDR3

общим объёмом до 2 Гбайт

- Модуль форм-фактора AMC Single Mid-Size/Full-Size, соответствующий

стандартам PICMG: AMC.0 R2.0, AdvancedMC.1 R2.0, AMC.2 R1.0 и AMC.4 R1.0

- Разъём расширения FMC (HPC FMC) для мезонинных модулей,

скорость передачи данных в FPGA до 75 Гбит/с

- Поддержка широкого спектра межмодульных интерфейсов: PCIe,

SRIO, XAUI, Gigabit Ethernet, SATA

Описание

Особенности

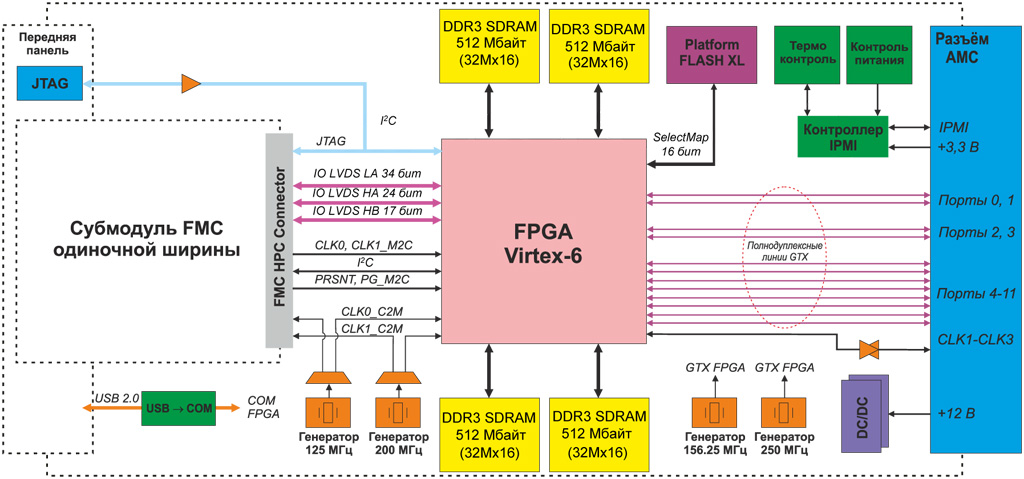

Модуль SAMC-713 форм-фактора Single Mid-Size/Full-Size AMC разработан на основе современной

высокопроизводительной FPGA Xilinx Virtex-6 семейств LXT и SXT и сочетает большой

выбор межмодульных интерфейсов и колоссальный объём внешней памяти. Установленный на модуле разъём

расширения стандарта FMC (ANSI/VITA 57.1-2010) позволяет использовать широкий

спектр мезонинных модулей: АЦП/ЦАП, оптические приемопередатчики и многие

другие.

Высокая производительность

Модуль SAMC-713 разработан для приложений, требующих высокую производительность, высокую

скорость передачи данных и низкую латентность. Модуль использует максимум возможностей FPGA

Xilinx Virtex-6, что определяет SAMC-713 как идеальный инструмент для значительного

снижения затрат на разработку, создание и эксплуатацию систем для программно-управляемого радио

SDR, современных телекоммуникационных, NGN, промышленных и медицинских приложений,

задач обработки данных. Установленный на модуле разъём расширения FMC позволяет использовать

почти неограниченные возможности, предлагаемые мезонинными модулями FMC.

Области применения

Сочетание высокопроизводительной FPGA Xilinx Virtex-6 семейств LXT (вплоть до VLX365T)

или SXT (вплоть до VSX475T), четырех независимых 16-битных банков памяти DDR3

SDRAM объёмом 512 Мбайт (общий объём памяти DDR3 2 Гбайт) и двенадцати высокоскоростных

полнодуплексных последовательных приёмопередатчиков GTX, обеспечивающих поддержку PCIe,

SRIO, XAUI, Gigabit Ethernet, SATA и других интерфейсов, совместно с поддержкой

CLK1, CLK2 и CLK3 предоставляет производителям оборудования, использующим модуль SAMC-713

высокоэффективное решение для широкого диапазона приложений: ЦОС, телекоммуникационных,

обработки данных, промышленных и медицинских.