Основные характеристики

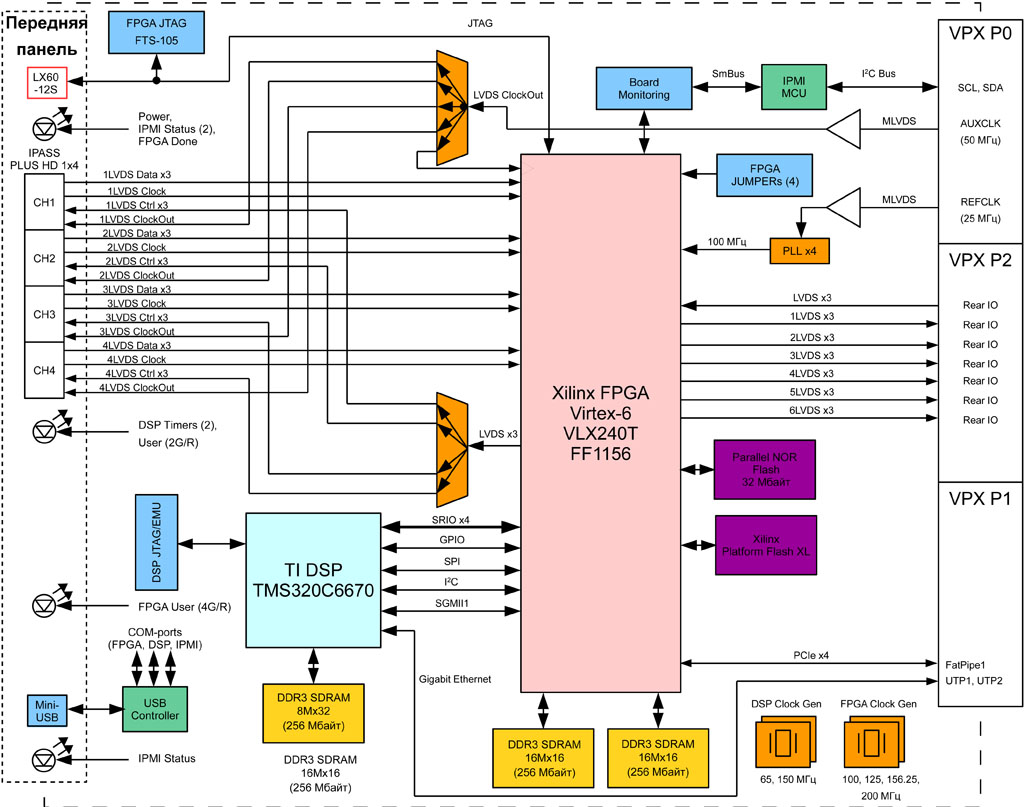

- Высокопроизводительная FPGA Xilinx

Virtex-6 семейства LXT/SXT в корпусе FF1156 с поддержкой кристаллов вплоть до VLX365T - Память FPGA — два

16-и разрядных банка DDR3 SDRAM по 256 Мбайт каждый - Четырёхъядерный DSP C6670 Texas Instruments (TI) c тактовой частотой 1,2 ГГц и набором сопроцессоров и ускорителей

- Память DSP —

64-х разрядный банк DDR3 SDRAM 256 Мбайт - Модуль

форм-фактора VPX 3U, соответствующий стандартам: ANSI/VITA46.0-2013 (воздушное охлаждение), ANSI/VITA46.3-2012 , ANSI/VITA46.6-2013 и ANSI/VITA65-2010 (R2012) - Цифровой порт сигналов LVDS передней панели на разъёме iPass+ HD 4x

- Системные интерфейсы: PCIe x4 2.0 / SRIO x4, двухканальный Gigabit Ethernet

- Шина тыльного ввода/вывода LVDS на разъёме VPX P2

Описание

Особенности

Модуль

Производительность

Наряду с высокой производительностью модуль имеет развитые системные интерфейсы: два канала Gigabit Ethernet через порты UTP1, UTP2 и, настраиваемый пользователем, канал PCIe 2.0 x4 / SRIO x4 через порт FP 1. Модуль предоставляет пользователю возможность организации межплатного взаимодействия, либо ввода/вывода высоко-скоростных сигналов модуля тыльного расширения через шину LVDS на разъёме P2 VPX. Цифровой порт iPass+ HD 4x Molex на передней панели предназначен для приёма данных LVDS от внешнего удаленного источника цифровых данных, в т. ч. АЦП.

Области применения

Поддержка модулем ряда системных функций OpenVPX: тактирование и синхронизация через объединительную плат, географическая адресация и т. д., значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы VPX для телекоммуникационных, промышленных и военных применений.

Модуль