Основные характеристики

- Основная FPGA Xilinx

Virtex-4 семейства VLX или VSX в корпусе FF1148 - Интерфейсная FPGA Xilinx

Virtex-4 семейства VLX или VSX в корпусе FF668 - Двухканальное аналого-цифровое преобразование

- Четыре банка памяти высокоскоростной статической RAM ZBT SRAM на FPGA, объёмом 9 Мбайт каждый

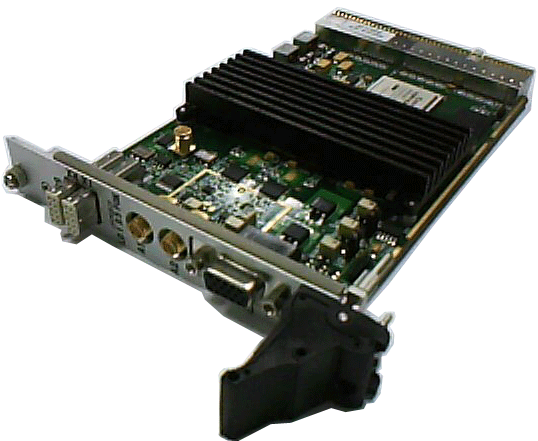

- Модуль форм-фактора CompactPCI 3U шириной 4HP c системным интерфейсом PCI 32/64 бита/33 МГц

Описание

Особенности

Модуль XDSP-57 форм-фактора CompactPCI 3U разработан на основе двух высокопроизводительных

FPGA Xilinx: основной

Интеграцию модуля с остальными модулями CompactPCI нашего производства облегчает наличие дуплексного

канала LVDS c производительностью не менее

Высокая производительность

Модуль XDSP-57 разработан для приложений, требующих высокую производительность, высокую скорость

передачи данных и низкую латентность. Модуль использует максимум возможностей FPGA Xilinx

Области применения

Модуль-ускоритель обработки данных XDSP-57 предназначен для выполнения двухканального