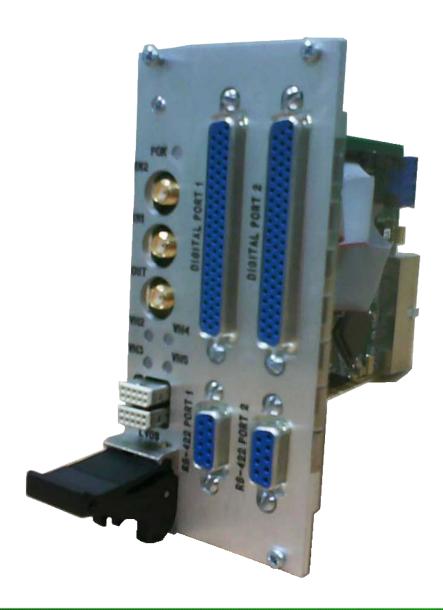

XDSP-53

Коммуникационный модуль на базе FPGA Xilinx Spartan-3 с поддержкой буферизованных портов ввода/вывода форм-фактора CompactPCI 3U

## Основные особенности

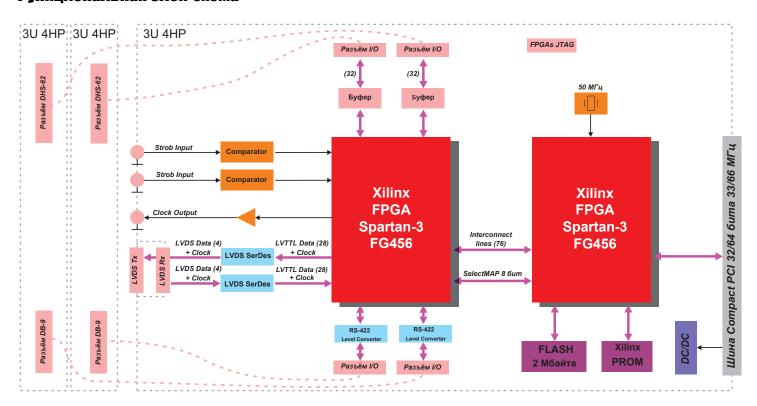

- Основная FPGA Xilinx Spartan-3 в корпусе FG456 из ряда: XC3S400, XC3S1000, XC3S1500, XC3S2000

- Интерфейсная FPGA Xilinx Spartan-3 в корпусе FG456 из ряда: XC3S400, XC3S1000

- Два компаратора внешнего стробирования: +1,5±0,1 В, либо +2,35±0,1 В

- Два буферизованных цифровых порта и два последовательных коммуникационных порта RS-422

- Канал приёма/передачи данных стандарта LVDS

- Модуль форм-фактора CompactPCI 3U 4–12HP с системным интерфейсом PCI 32 бита/33 МГц, соответствующий стандарту PICMG 2.0 Rev 3.0

## Обзор модуля

#### Особенности

Модуль XDSP-53 выполнен в конструктиве CompactPCI 3U с поддержкой системного интерфейса PCI 32 бита/33 МГц. Количество занимаемых слотов: от 1 до 3 (4–12 HP) в зависимости от конфигурации передней панели (вывода на неё цифровых портов).

#### Особенности

Модуль XDSP-53 разработан для приложений, требующих высокую производительность, высокую скорость передачи данных и низкую латентность. Модуль использует максимум возможностей FPGA Xilinx Spartan-3.

Модуль имеет дуплексный канал LVDS с производительностью не менее 1,8 Гбит/с в каждую сторону.

### Области применения

Модуль XDSP-53 форм-фактора CompactPCI 3U предназначен для решения задач управления периферийными устройствами посредством буферизованных портов ввода/вывода (до 64-х линий), интерфейсного обмена через порты RS-422, а также формирования/приёма стробирующих и тактовых синхросигналов.

## Функциональная блок-схема

## Технические характеристики

#### **FPGA**

Основная Xilinx Spartan-3 в корпусе FG456 из ряда:

• XC3S400, XC3S1000, XC3S1500, XC3S2000.

#### Особенности основной FPGA:

- свыше 46 тыс. логических ячеек (XC3S2000);

- до 40 аппаратных умножителей FPGA 18 × 18 бит (XC3S2000);

- до 40 банков двухпортового синхронного RAM по 18 кбит общим объёмом 720 кбит (XC3S2000);

- четыре DCM FPGA.

Интерфейсная Xilinx Spartan-3 в корпусе FG456 из ряда:

XC3S400, XC3S1000.

### Особенности интерфейсной FPGA:

- свыше 17 тыс. логических ячеек;

- до 24 аппаратных умножителей FPGA 18 × 18 бит;

- до 24 банков двухпортового синхронного RAM по 18 кбит общим объёмом 432 кбит (XC3S2000);

- четыре DCM FPGA.

#### Память

Для основной FPGA: NOR Flash 2 Мбайта (до 8 Мбайт)

Для интерфейсной FPGA: Xilinx Serial Platform Flash 256 Кбайт

### Соответствие стандартам

PICMG 2.0 Rev 3.0 CompactPCI Base Specification

### Тактирование

Опорный кварцевый генератор 50 МГц/1000 ррт

Встроенные компараторы внешнего стробирования (2 канала):

- вход: открытый по постоянному току;

- входное сопротивление коммутируемое, Ом:

- 1000±100 в отсутствии перемычек SW9, SW10;

- 50±5 при установленных перемычках SW9, SW10.

- задержка распространения сигнала до FPGA, нс, не более 20;

- максимальный уровень внешнего сигнала в пределах от -0,5...+5,5 B;

- порог срабатывания коммутируемый: +1,5±0,1 В или +2,35±0,1 В.

Встроенный буфер внешнего тактирования:

- выходное сопротивление коммутируемое: 25-50±5 Ом;

- размах выходного напряжения на нагрузке:

- 50 Ом, +0,2...+5 В;

- 10 кОм, +0,2...+10 В.

- предельная частота тактирования не менее 50 МГц.

### Интерфейсы

Два буферизованных цифровых порта:

- число линий ввода/вывода с побайтным разбиением направления передачи: 32;

- стандарт ввода/вывода коммутируемый: ТТЛ 3,3 В или 5 В;

- номинальный ток нагрузки по каждой линии порта: 24 мА (48 линий) и 48 мА (16 линий);

- задержка распространения сигнала на ввод/вывод не более 15 нс.

Два последовательных коммуникационных порта:

- тип порта: RS-422, полнодуплексный;

- номинальная пропускная способность 115 кбит;

- предельная пропускная способность не менее 10 Мбит.

Каналы приема/передачи данных стандарта LVDS:

- организация: четыре пары данных + пара тактирования;

- предельная пропускная способность не менее 1820 Мбит;

- разрядность принятых данных в стандарте LVTTL 28 бит;

- минимальная частота тактирования данных LVTTL 20 МГц.

Поддержка интерфейса инициализации FPGA JTAG IEEE 1149.1 2,5 B

### Энергопотребление

Потребляемая мощность интерфейсного модуля не более 27 Вт

Распределение потребляемой мощности по линиям питания:

- +12 В: до 0,09 A (1,1 Вт);

- -12 В: до 0,09 A (1,1 Вт);

- +5 В: до 3 A (15 Вт);

- +3,3 В: до 3 А (10 Вт).

## Условия эксплуатации

Охлаждение: воздушное

Диапазон рабочих температур: коммерческий (0...+50 °C) или индустриальный (-40...+85 °C)

Температура хранения: -40...+85 °C

Влажность: 10-95 % без конденсата

## Размеры

Форм-фактор: CompactPCI 3U

Ширина: 4-12НР (от 1 до 3-х слотов)

Размеры Mid-Size: 100 × 160 × 30 мм

## Информация для заказа

Основная FPGA Xilinx

Spartan-3 в корпусе FG456

FM400: XC3S400 FM1000: XC3S1000 FM1500: XC3S1500

FM2000: XC3S2000

II Chymeonari i Ch

FS400: XC3S400 FS1000: XC3S1000

Spartan-3 в корпусе FG456

Исполнение (температурный диапазон)

Служебная FPGA Xilinx

**Т0:** Коммерческое (0...+50 °C) **Т1:** Индустриальное (-40...+85 °C)

1 4

Покрытие

CV0: Без влагозащитного покрытия CV1: С влагозащитным покрытием

Пример кода изделия: **XDSP-53-FM400-FS400-T1-CV1**

XDSP-53 — Коммуникационный модуль на базе FPGA Xilinx Spartan-3 с поддержкой буферизованных портов ввода/вывода

форм-фактора CompactPCI 3U Основная FPGA Xilinx: XC3S400 Служебная FPGA Xilinx: XC3S400

Исполнение (температурный диапазон): Индустриальное (-40...+85 °C)

Покрытие: С влагозащитным покрытием

Возможны другие конфигурации модуля по индивидуальному запросу. За дополнительной информацией обращайтесь в SET.

# Контактная информация

ЗАО «Скан Инжиниринг Телеком» Россия, 394030, г. Воронеж, ул. Свободы, 75 Тел.: +7 (473) 272-71-01, факс.: +7 (473) 251-21-99 www.setdsp.ru

Электронная почта:

Отдел продаж: sales@setdsp.ru

ООО «Скан Инжиниринг Телеком - СПб» Россия, 199106, г. Санкт-Петербург, 22-я линия В.О., д. 3, корп. 1, лит. М. Тел.: +7 (812) 406-99-95, +7 (812) 406-99-96 www.setdsp.ru

Электронная почта:

Отдел продаж: sales.spb@setdsp.ru

ЗАО «Скан Инжиниринг Телеком». Все права защищены. © 1991–2018 Документ DS-XDSP-53 1.0 создан в ООО «Скан Инжиниринг Телеком - СПб». Все права защищены. © 2018